Tech Elements

Радиоэлектроника и телекоммуникации

Приемное устройство телесигнализации

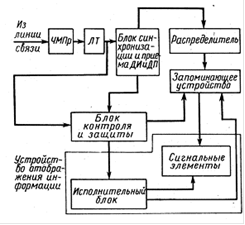

В приемном устройстве телесигнализации (рис. 5) частотные импульсы из линии связи поступают на ЧМ приемник (ЧМПр), где преобразуются в серию прямоугольных импульсов и пауз. Из частотного приемника серия через линейный триггер ЛТ и блок синхронизации поступает на распределитель. Одновременно с линейного триггера импульсы поступают на блок контроля и защиты.

Распределитель переключается в соответствии с тактовой серией импульсов. Выходные цепи распределителя открываются только при приеме длинных импульсов (или пауз). Импульсы с распределителя поступают в запоминающее устройство. Блок контроля и защиты в течение всего цикла передачи осуществляет контроль получаемой тактовой серии. Если при передаче не возникало искажений, в конце цикла производится считывание информации с запоминающего устройства, которая и поступает на сигнальные элементы. Управление запоминающим устройством и сигнальными элементами осуществляется исполнительным блоком, который в свою очередь получает командные импульсы после проверки правильности передачи блоком контроля и защиты.

Распределитель выполнен по той же схеме, что и распределитель передающего полукомплекта (см. рис. 4). В выходных цепях его вместо контактов-датчиков включены обмотки записи магнитных элементов с прямоугольной петлей гистерезиса, выполняющих роль запоминающего устройства.

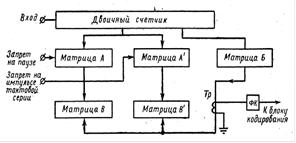

Рис. 4. Структурная схема распределителя устройства ТС КП

Распределитель применен матричный, состоящий из шестиразрядного двоичного счетчика и двухступенчатого параллельно-последовательного матричного дешифратора (матрицы А, А', Б, В и В' на рис. 4). Первая ступень дешифратора содержит два диодных дешифратора трехразрядного двоичного кода А и А' с прямыми выходами, аналогичный дешифратор с инверсным выходом Б и два последовательных матричных дешифратора В и В'.

Матрицы А, А' и Б имеют по восемь выходных цепей. Матрицы А и А' каждая в комбинации с матрицей Б образуют 64 выходные цепи. Таким образом, общее число выходных цепей -128. Матрица А включается в работу при импульсе, матрица А' - при паузе. Это осуществляется путем снятия в соответствующий момент времени запрещающего потенциала с шинки запрета.

В выходных цепях матриц В и В' осуществляющих контроль соответственно на импульсах и паузах тактовой серии, включены контакты-датчики телесигнализации, а в выходных цепях матрицы Б - трансформаторы Тр. При замкнутом контакте-датчике импульс тока через трансформатор Тр и формирующий каскад ФК поступает на блок кодирования.

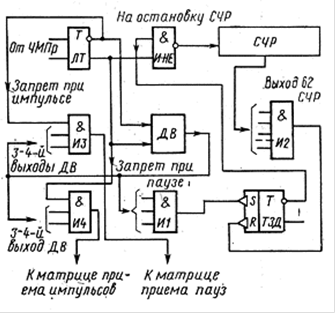

Блок синхронизации и приема длинных импульсов и пауз состоит из триггера задержки ТЗД (рис. 6), элемента И-НЕ и датчика времени ДВ. Датчик времени (рис. 7, а) представляет собой трехразрядный двоичный счетчик на триггерах Т1 - ТЗ со схемой сброса, выполненной на транзисторных каскадах задержки Тз1, Тз2 и усилителе УС. Счетчик приводится в действие мультивибратором MB.

На вход счетчика поступают импульсы мультивибратора с постоянной частотой. Измерение времени осуществляется путем отсчета числа импульсов мультивибратора. Счетчик сбрасывается в нулевое положение в начале каждого импульса и паузы тактовой серии и начинает отсчет числа импульсов мультивибратора. Сброс счетчика осуществляется транзисторными каскадами задержки Тз1 или Тз2, воздействующими через схему ИЛИ на усилитель УС - соответственно на импульсе и паузе. Вначале импульса тактовой серии импульс, поступающий с линейного триггера, запускает каскад задержки Тз1, который на время разряда конденсатора С1 закрывается. При этом импульс с коллектора транзистора через схему ИЛИ поступает на усилитель, который сбрасывает счетчик в нулевое положение. После разряда конденсатора С1 каскад Тз2 открывается, снимая импульс сброса. Начинается отсчет импульсов. Аналогично работает каскад Тз2 на паузе.

Частота мультивибратора в приемном устройстве телесигнализации выбрана такой, что за время короткого импульса датчик времени успевает отсчитать не более одного импульса, на длинном импульсе - 3-4 импульса, а на сверхдлинном - 7 импульсов и более (см. временную диаграмму на рис. 7, б).

Рис. 5. Структурная схема устройства ТС ДП

Рис. 6. Блок синхронизации и приема длинных импульсов

Нормально серия импульсов с линейного триггера через схему И-НЕ поступает на вход счетчика распределителя СЧР (см. рис. 6), который при этом переключается. В момент, когда распределитель переходит в 63-ю позицию, импульс, поступающий со схемы И2, возбуждает триггер задержки, который выдает импульс, запирающий элемент И-НЕ. Поступление кодовой серии на счетчик распределителя прекращается. Если работа приемного устройства была синфазной, то с 63-й позицией распределителя должен был совпасть сверхдлинный фразирующий импульс. Датчик времени в этом случае доходит до 7-го положения и через схему совпадений И1 осуществляет сброс триггера задержки. Так как сброс триггера ТЗД происходит до окончания сверхдлинного импульса, то после его сброса транзистор схемы И-НЕ вновь открывается и счетчик распределителя переключается в 63-ю позицию. Этим восполняется недостающий в тактовой серии 64-й импульс.

Другие стьтьи в тему

Разработка кабельной магистрали для организации многоканальной связи различного назначения на участке г. Биробиджан – УАК10

Научно-технический прогресс во многом

определяется скоростью передачи информации и ее объемом. Возможность резкого

увеличения объемов передаваемой информации наиболее полно реализуется в

результате применения волоконно-оптических линий связи (ВОЛС), которые по

сравнению с такими широ ...

Расчет надежности системы телемониторинга

Системы СЖАТ (системы железнодорожной автоматики и телемеханики)

предназначены для регулирования движения поездов с целью решения таких важных задач,

как обеспечение безопасности движения поездов и повышение эффективности

перевозочного процесса. Уровень надежности СЖАТ непосредственно ...

Разделы

- Главная

- Радиоэлектроника и телекомуникации в современном мире

- Разработка проекта системы видеонаблюдения

- Разработка схемы радиовещательного приемника

- Разработка телевизионного приемника

- Разработка цифрового дешифратора

- Производство полупроводниковых приборов

- Развитие технологий передачи данных

- Разработка домашней охранной сигнализации