Tech Elements

Радиоэлектроника и телекоммуникации

Параметры триггеров

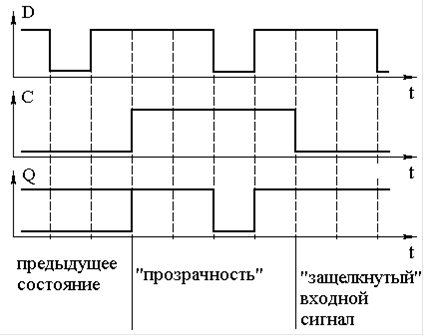

Рис. 21. Временная диаграмма D триггера (защелки)

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название - триггер-защелка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Другие стьтьи в тему

Разработка стенда для исследования схемы синхронного RS-триггера

Одним

из ведущих направлений развития современной микроэлектроники элементной базы

являются большие интегральные микросхемы памяти, которые служат основой для

построения запоминающих устройств в аппаратуре различного назначения. Наиболее

широкое применение эти микросхемы нашли в ЭВМ, ...

Разработка схем приемного и передающего устройств

В

цифровых системах сигналы передаются в виде различных комбинаций импульсов

постоянной амплитуды, отображающих числовое значение сигнала в каждый данный

момент времени (кодовыми группами).

Чтобы

каждое значение сигнала можно было преобразовать в соответствующую кодовую

группу, к ...

Разделы

- Главная

- Радиоэлектроника и телекомуникации в современном мире

- Разработка проекта системы видеонаблюдения

- Разработка схемы радиовещательного приемника

- Разработка телевизионного приемника

- Разработка цифрового дешифратора

- Производство полупроводниковых приборов

- Развитие технологий передачи данных

- Разработка домашней охранной сигнализации