Tech Elements

Радиоэлектроника и телекоммуникации

Генератор чисел на базе двоичного счетчика

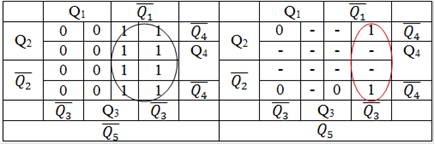

D5=Q1Q2Q3Q4![]()

![]()

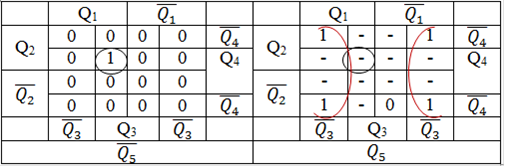

D4=![]()

![]() Q4

Q4![]()

![]() Q4

Q4![]()

![]() Q4

Q4![]()

![]() Q1Q2Q3

Q1Q2Q3![]()

![]()

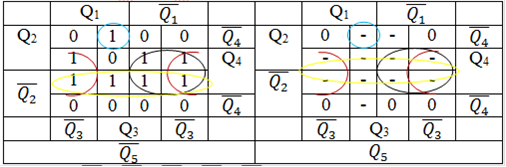

D3=Q1Q2![]()

![]() Q3

Q3![]()

![]() Q3

Q3![]()

![]()

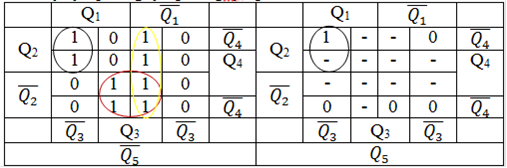

D2=Q1![]()

![]() Q2

Q2

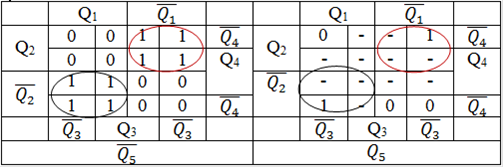

D1=![]()

![]()

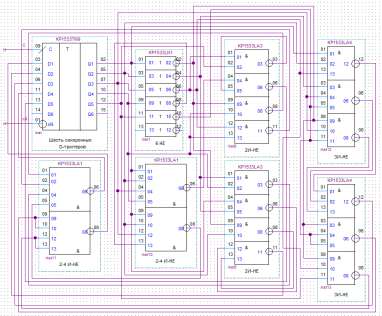

Схема параллельного двоичного счетчика на базе D-триггера с модулем пересчета 21, в ней используются ИМС КР1533ЛН1, КР1533ЛА3, КР1533ЛА1, КР1533ЛА4 и КР1533ТМ9.

Схема счётчика представлена на рисунке 7.

Рисунок 7 - Параллельный двоичный счетчик на базе D-триггера.

Нагрузка по току со стороны источника входного сигнала начальной установки:

Iвх1( R ) = 0,02мА, Iвх0( R ) = 0,1мА.

Нагрузка по току со стороны источника входного сигнала синхроимпульса:

Iвх1(С) = 0,02мА, Iвх0(С) =0,1мА.

По нагрузке на входные сигналы данная схема удовлетворяет условиям ТЗ.

Время формирования выходных сигналов счетчика по входу «R» (Тформ.R) равно tпер.(КР1533ТМ9) по входу «R» = 23 (нс).

Задержка переключения счетчика по входу «R» (Тпер.R) равна tпер.(КР1533ТМ9) по входу «R» + tпер.( КР1533ЛН1) + tпер.(КР1533ЛА4)+tпер.(КР1533ЛА1) + время опережения установки информации по входам «J» и «K» относительно фронта спада на входе «С» триггера = 23+11+11+11+10 =66нс.

Время формирования выходных сигналов счетчика по входу «С» (Тформ.С) равно tпер.(КР1533ТМ9) по входу «С» = 17 (нс).

Задержка переключения счетчика по входу «С» (Тпер.С) равна tпер.(КР1533ТМ9) по входу «С» + tпер.( КР1533ЛН1) + tпер.(КР1533ЛА4)+tпер.(КР1533ЛА1) + время опережения установки информации по входам «J» и «K» относительно фронта спада на входе «С» триггера = 17+11+11+11+10 =60нс.

. Построение двоичного суммирующего счетчика с модулем пересчета 21 на базе СИС КР1533ИЕ19

Таблица истинности для функции обнуления счетчика представлена в таблице 8.

Таблица 8.

|

N |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

F |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

2 |

0 |

0 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0 |

1 |

0 |

0 |

|

4 |

0 |

0 |

0 |

1 |

1 |

0 |

|

5 |

0 |

0 |

1 |

0 |

0 |

0 |

|

6 |

0 |

0 |

1 |

0 |

1 |

0 |

|

7 |

0 |

0 |

1 |

1 |

0 |

0 |

|

8 |

0 |

0 |

1 |

1 |

1 |

0 |

|

9 |

0 |

1 |

0 |

0 |

0 |

0 |

|

10 |

0 |

1 |

0 |

0 |

1 |

0 |

|

11 |

0 |

1 |

0 |

1 |

0 |

0 |

|

12 |

0 |

1 |

0 |

1 |

1 |

0 |

|

13 |

0 |

1 |

1 |

0 |

0 |

0 |

|

14 |

0 |

1 |

1 |

0 |

1 |

0 |

|

15 |

0 |

1 |

1 |

1 |

0 |

0 |

|

16 |

0 |

1 |

1 |

1 |

1 |

0 |

|

17 |

1 |

0 |

0 |

0 |

0 |

0 |

|

18 |

1 |

0 |

0 |

0 |

1 |

0 |

|

19 |

1 |

0 |

0 |

1 |

0 |

0 |

|

20 |

1 |

0 |

0 |

1 |

1 |

0 |

|

21 |

1 |

0 |

1 |

0 |

0 |

1 |

|

22 |

1 |

0 |

1 |

0 |

1 |

* |

|

23 |

1 |

0 |

1 |

1 |

0 |

* |

|

24 |

1 |

0 |

1 |

1 |

1 |

* |

|

25 |

1 |

1 |

0 |

0 |

0 |

* |

|

26 |

1 |

1 |

0 |

0 |

1 |

* |

|

27 |

1 |

1 |

0 |

1 |

0 |

* |

|

28 |

1 |

1 |

0 |

1 |

1 |

* |

|

29 |

1 |

1 |

1 |

0 |

0 |

* |

|

30 |

1 |

1 |

1 |

0 |

1 |

* |

|

31 |

1 |

1 |

1 |

1 |

0 |

* |

|

32 |

1 |

1 |

1 |

1 |

1 |

* |

Другие стьтьи в тему

Разработка кабельной системы

Структурированная кабельная система (СКС), по мнению

большинства специалистов по информационным технологиям, является в настоящее

время неотъемлемой частью любого современного общественного здания, а ее

отсутствие, рассматриваемое управленческим и техническим персоналом как

анахрониз ...

Расчет словесной разборчивости речи по методу Покровского Н.Б. Система защиты речевой информации

Человеческая речь является одним из важнейших путей

информационного взаимодействия. При децентрализации экономической и

политической систем и соответствующем увеличении доли оперативной информации,

непосредственно связывающей самостоятельных в принятии решений людей,

значимость речев ...

Разделы

- Главная

- Радиоэлектроника и телекомуникации в современном мире

- Разработка проекта системы видеонаблюдения

- Разработка схемы радиовещательного приемника

- Разработка телевизионного приемника

- Разработка цифрового дешифратора

- Производство полупроводниковых приборов

- Развитие технологий передачи данных

- Разработка домашней охранной сигнализации